# LM1204 150 MHz RGB Video Amplifier System

## **General Description**

The LM1204 is a triple 150 MHz video amplifier system designed specifically for high resolution RGB video display applications. In addition to three matched video amplifiers, the LM1204 contains a DC operated contrast control, a DC operated drive control for each amplifier, and a dual clamping system for both brightness control and video blanking. The LM1204 also contains a back porch clamp pulse generator which is activated by an externally supplied  $\pm \rm H/HV$  sync signal or by an external composite video signal. The  $\pm \rm H/HV$  sync input will have priority over the composite video input. A single  $- \rm H/HV$  sync output is provided for the automatically selected sync input signal. The back porch clamp pulse width is user adjustable from 0.3  $\mu s$  to 4  $\mu s$ .

The LM1204 video output stage will directly drive most Hybrid or discrete CRT amplfier input stages without the need for an external buffer transistor. The device has been designed to operate from a 12V supply with all DC controls operating over a 0V to 4V range providing for an easy interface to serial digital buss controlled monitors.

### **Features**

- Built-in video blanking function

- Built-in sync separator for composite video input

- Includes DC restoration of video signals

- Back porch clamp pulse width user adjustable

- DC control of brightness, contrast, blanking level, drive and cutoff

- DC controls are 0V to 4V for easy interfacing to a digitally controlled system

## **Key Specifications**

- 150 MHz large signal bandwidth (typ)

- 2.3 ns rise/fall times (typ)

- 0.1 dB contrast tracking (typ)

- ±3 dB drive (Δ gain) adjustments on R, G, B channels (typ)

## **Applications**

- High resolution CRT monitors

- Video AGC amplifier

- Wideband amplifier with gain and DC offset control

31 V<sub>CC</sub>

29 GND

30 G VIDEO OUT

+/- HSYNC

27

OND GN

+/- H SYNC IN BLANK GATE IN NTEGRATOR CAP

## **Block Diagram and Connection Diagram** Top View 3 4 CONTRAST 38 R FEEDBACK B CLAMP CAP 10 36 V<sub>CC</sub> CONTRAST 35 B VIDEO OUT Δ GAIN ADJ 34 GND 33 B FEEDBACK B Δ GAIN 13 CONTRAST A GAIN ADJ. 32 G BLANKING CAP G CLAMP CAP 14

GND 16

G VIDEO IN 17

Ordering Information

Order Number LM1204V See NS Package Number V44A

BLANKING

BRIGHTNESS

INESS

TL/H/11238-1

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage, V<sub>CC</sub> Pins 2, 4, 6, 19, 31, 41, 44 (Note 3) 13.5V

Peak Video Output Source Current

(Any One Amplifier) Pins 30, 35 or 39 30 mA

$\text{GND} \leq \text{V}_{IN} \leq \text{V}_{CC}$ Voltage at Any Input Pin, V<sub>IN</sub> 5.5 V<sub>PP</sub>

Maximum ±H Sync Input Voltage

Power Dissipation, PD (Above 25°C

2.4W Derate Based on  $\theta_{JA}$  and  $T_{J}$ )

Thermal Resistance,  $\theta_{JA}$ 52 °C/W Junction Temperature,  $T_J$ 150°C ESD Susceptibility (Note 4) 2.5 kV Storage Temperature  $-65^{\circ}\text{C}$  to  $150^{\circ}\text{C}$ Lead Temperature Vapor Phase (60 seconds) 215°C Infrared (15 seconds) 220°C

## **Operating Ratings** (Note 2)

Temperature Range 0°C to 70°C Supply Voltage, V<sub>CC</sub>  $10.8V \leq V_{CC} \leq 13.2V$

## **DC Electrical Characteristics (Video Amplifier Section)**

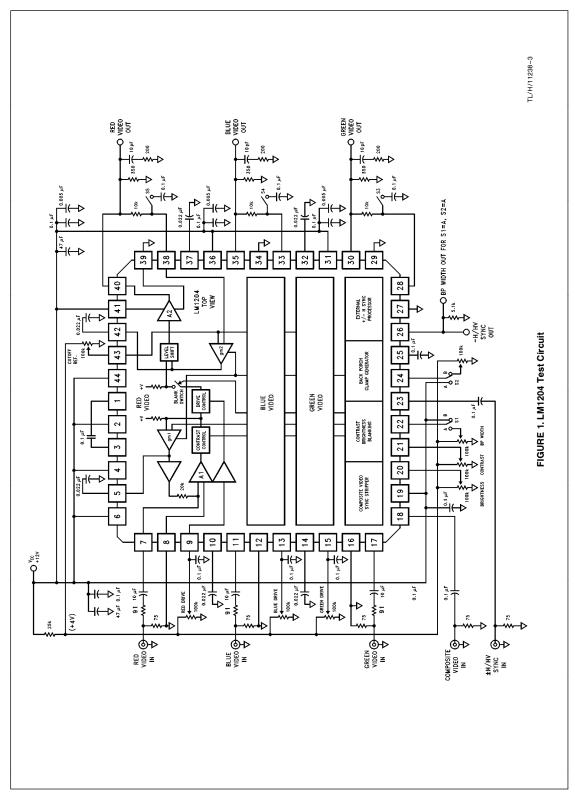

The following specifications apply for  $V_{CC}$  (pins 2, 4, 6, 19, 31, 36, 41 and 44) = 12V and  $T_A$  = 25°C unless otherwise specified. S1 = B, S2 = B, S3, 4, 5 closed, V9, 13, 15 = 2V, V20, 21, 22, 24, 43 = 0.5V unless otherwise specified; see test circuit, Figure 1.

| Symbol               | Parameter                                           | Conditions                                      | Typical<br>(Note 5) | Limit<br>(Note 6) | Units       |

|----------------------|-----------------------------------------------------|-------------------------------------------------|---------------------|-------------------|-------------|

| Is                   | Supply Current                                      | No Video or Sync Input<br>Signals, S1 = A       | 100                 | 125               | mA<br>(Max) |

| Ι <sub>Β</sub>       | Input Bias Current<br>(Pin 9, 13, 15, 20, 21 or 22) | S1 = A                                          | 0.3                 | 2                 | μΑ<br>(Max) |

| I <sub>24h</sub>     | Blank Gate Input High Current                       | V24 = 4V                                        | 0.01                | 2                 | μΑ<br>(Max) |

| l <sub>24l</sub>     | Blank Gate Input Low Current                        | V24 = 0V                                        | 2                   | 5                 | μΑ<br>(Max) |

| I <sub>FB</sub>      | Feedback Input Current<br>(Pin 28, 33 or 38)        |                                                 | 150                 |                   | nA          |

| I <sub>Blank+</sub>  | Blank Cap Charge Current                            | $V_{32,37,42} = 0V$                             | 185                 | 75                | μΑ (Min)    |

| I <sub>Blank</sub> – | Blank Cap Discharge Current                         | $V_{32,37,42} = 5V$                             | -185                | -75               | μΑ (Min)    |

| I <sub>BB</sub>      | Blank Cap Bias Current (Pins 32, 37, 42)            |                                                 | 20                  |                   | nA          |

| I <sub>Clamp+</sub>  | Clamp Cap Charge Current                            | $V_{5,10,14} = 0V$                              | 185                 | 75                | μΑ (Min)    |

| I <sub>Clamp</sub> – | Blank Cap Discharge Current                         | $V_{5,10,14} = 5V$                              | -185                | -75               | μΑ (Min)    |

| I <sub>CB</sub>      | Clamp Cap Bias Current (Pins 5, 10, 14)             |                                                 | 20                  |                   | nA          |

| V <sub>24h</sub>     | Blank Gate High Input Voltage                       | Input Signal is Not Blanked                     |                     | 2                 | V (Min)     |

| $V_{24I}$            | Blank Gate Low Input Voltage                        | Input Signal is Blanked                         |                     | 0.8               | V (Max)     |

|                      | Blank Comparator Offset Voltage                     | Voltage between V43 and<br>Any One Video Output | 2                   | 50                | mV<br>(Max) |

| V <sub>H</sub>       | Video Output High Voltage<br>(Pins 30, 35, 40)      | $R_L = 350\Omega$<br>V28, 33, 38 = 0V           | 8.7                 | 7                 | V(Min)      |

| V <sub>L</sub>       | Video Output Low Voltage<br>(Pins 30, 35, 40)       | $R_L = 350\Omega$<br>V28, 33, 38 = 4V 0.1 0.5   |                     | 0.5               | V(Max)      |

| V <sub>CM43</sub>    | Common Mode Range of Blank                          |                                                 |                     | 0.5               | V(Min)      |

|                      | Comparator (Pins 43, 28, 33, 38)                    |                                                 |                     | 4                 | V(Max)      |

DC Electrical Characteristics (Sync Separator/Processor Section) The following specifications apply for  $V_{CC}$  (Pins 2, 4, 6, 19, 31, 36, 41 and 44) = 12V and  $T_A = 25^{\circ}C$ , unless otherwise specified. S1 = B, S2 = B, S3, 4, 5 closed, V9, 13, 15 = 2V, V20, 21, 22, 24, 43 = 0.5V, unless otherwise specified; see Test Circuit Figure 1.

| Symbol             | Parameter                                | Conditions | Typical<br>(Note 5) | Limit<br>(Note 6) | Units  |

|--------------------|------------------------------------------|------------|---------------------|-------------------|--------|

| −H V <sub>OH</sub> | −H Sync Output Logic High (Pin 26)       |            | 4.2                 | 2.4               | V(Min) |

| −H V <sub>OL</sub> | −H Sync Output Logic Low (Pin 26)        |            | 0.1                 | 0.4               | V(Max) |

| V <sub>23</sub>    | Quiescent DC Voltage at ±H<br>Sync Input |            | 3                   |                   | V      |

AC Electrical Characteristics (Video Amplifier Section) The following specifications apply for  $V_{CC}$  (Pins 2, 4, 6, 19, 31, 36, 41 and 44) = 12V and  $T_A$  = 25°C, unless otherwise specified. S1 = B, S2 = B, S3, 4, 5 closed, V9, 13, 15, 21, 24, 43 = 4V, V20 = 2V, unless otherwise specified; see Test Circuit

| Symbol                     | Parameter                                          | Conditions                                                 | Typical<br>(Note 5) | Limit<br>(Note 6) | Units    |

|----------------------------|----------------------------------------------------|------------------------------------------------------------|---------------------|-------------------|----------|

| R <sub>IN</sub>            | Video Amplifier Input Resistance                   |                                                            | 20                  |                   | kΩ       |

| A <sub>Vmax</sub>          | Maximum Video Amplifier Gain                       | f <sub>IN</sub> = 12 kHz                                   | 10                  | 5.5               | V/V(Min) |

| ΔA <sub>Vtrack</sub>       | Amplifier Gain (Contrast)<br>Tracking (Note 7)     |                                                            | 0.1                 |                   | dB       |

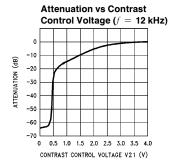

| $\Delta A_{V2V}$           | Attenuation at 2V                                  | Ref: A <sub>Vmax</sub> V21 = 2V                            | 6                   |                   | dB       |

| ΔA <sub>V0.5V</sub>        | Attenuation at 0.5V                                | Ref: A <sub>Vmax</sub> V21 = 0.5V                          | 28                  | 20                | dB(Min)  |

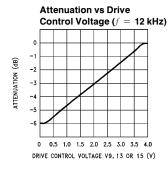

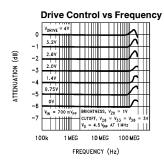

| ΔGain                      | Δ Gain Range (Pins 9, 13, 15)                      | V9, 13, 15 = 0V to 4V                                      | ±3                  |                   | dB       |

| $\Delta V_{O}$             | Max Brightness Tracking Error (Note 8)             |                                                            | 100                 |                   | mV       |

| f-3 dB                     | Video Amplifier Bandwidth (Note 9)                 | $V_{OUT} = 3.5 V_{PP}$                                     | 150                 |                   | MHz      |

| THD                        | Video Amplifier Distortion                         | $V_{OUT} = 1 V_{PP}, f = 12 kHz$                           | 0.3                 |                   | %        |

| t <sub>R</sub>             | Video Output Rise Time (Note 9)                    | Square Wave Input $V_{OUT} = 3.5 V_{PP}, R_L = 350 \Omega$ | 2.0                 |                   | ns       |

| t <sub>F</sub>             | Video Output Fall Time (Note 9)                    | Square Wave Input $V_{OUT} = 3.5 V_{PP}, R_L = 350 \Omega$ | 2.3                 |                   | ns       |

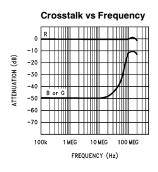

| V <sub>ISO (1 MHz)</sub>   | Video Amplifier 1 MHz<br>Isolation (Notes 9, 10)   |                                                            | -50                 |                   | dB       |

| V <sub>ISO</sub> (130 MHz) | Video Amplifier 130 MHz<br>Isolation (Notes 9, 10) |                                                            | -10                 |                   | dB       |

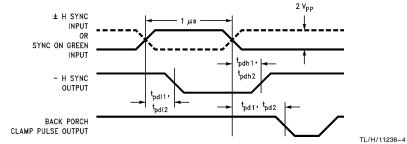

AC Electrical Characteristics (Sync Separator/Processor Section) The following specifications apply for  $V_{CC}$  (Pins 2, 4, 6, 19, 31, 36, 41 and 44) = 12V and  $T_A = 25^{\circ}C$ , unless otherwise specified. S1 = A, S2 = B, S3, 4, 5 closed, V9, 13, 15, 20, 21, 43 = 2V, unless otherwise specified; see Test Circuit Figure 1 and Timing Diagram for input waveform.

| Symbol                               | Parameter                                                               | Conditions                                             | Typical<br>(Note 5) | Limit<br>(Note 6) | Units                    |

|--------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------|---------------------|-------------------|--------------------------|

| V <sub>18(Min)</sub>                 | Composite Video Input Voltage<br>(Pin 18)                               | S2 = A, Input = 10% Duty<br>Cycle, Test for Loss of BP |                     | 0.15              | V <sub>PP</sub><br>(Min) |

| V <sub>18(Max)</sub>                 | Composite Video Input Voltage (Pin 18)                                  | Pulse at Pin 26                                        |                     | 2                 | V <sub>PP</sub><br>(Max) |

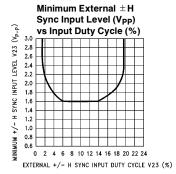

| V <sub>23</sub>                      | ± H Sync Input Voltage (Pin 23)                                         | Input = 10% Duty Cycle                                 |                     | 1.6               | V <sub>PP</sub><br>(Min) |

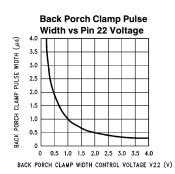

|                                      | Back Porch Clamp Pulse Width at V <sub>24</sub> = 1V                    | S2 = A, Pin 26 = BP Output                             | 1                   | 1.4               | μs<br>(Max)              |

|                                      | Back Porch Clamp Pulse Width at V <sub>24</sub> = 4V                    |                                                        | 300                 | 600               | ns<br>(Max)              |

|                                      | Maximum ±H Sync Input Frequency                                         |                                                        | 600                 |                   | KHz                      |

| D <sub>HI</sub>                      | Max Duty Cycle of Active High<br>H Sync (Pin 23)                        | Test for Loss of Sync<br>at Pin 26                     | 22                  |                   | %                        |

| D <sub>LO</sub>                      | Max Duty Cycle of Active Low<br>H Sync (Pin 23)                         |                                                        | 22                  |                   | %                        |

| t <sub>pdl1</sub>                    | ±H Sync Input to −H Sync<br>Output Low Delay                            | Input = 10% Duty Cycle                                 | 100                 |                   | ns                       |

| <sup>t</sup> pdh1                    | ±H Sync Input to -H Sync<br>Output High Delay                           | Input = 10% Duty Cycle                                 | 65                  |                   | ns                       |

| t <sub>pd1</sub>                     | ± H Sync Input Trailing Edge to<br>Back Porch Clamp Output Delay        | Input = 10% Duty Cycle,<br>S2 = A                      | 70                  |                   | ns                       |

| t <sub>pdl2</sub>                    | Composite Video Input to -H Sync Output Low Delay                       | Input = 10% Duty Cycle                                 | 106                 |                   | ns                       |

| t <sub>pdh2</sub>                    | Composite Video Input to -H<br>Sync Output High Delay                   | Input = 10% Duty Cycle                                 | 68                  |                   | ns                       |

| t <sub>pd2</sub>                     | Composite Video Input Trailing<br>Edge to Back Porch Clamp Output Delay | Input = 10% Duty Cycle<br>S2 = A                       | 78                  |                   | ns                       |

| t <sub>pdl2</sub> -t <sub>pdl1</sub> | Composite Video and ±H Sync Input to −H Sync Output Delta Delay         | Input = 10% Duty Cycle                                 | 6                   |                   | ns                       |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: V<sub>CC</sub> supply pins 2, 4, 6, 19, 31, 36, 41 and 44 must be externally wired together to prevent internal damage during V<sub>CC</sub> power on/off cycle.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Typical specifications are specified at +25°C and represent the most likely parametric norm.

Note 6: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 7:  $\Delta A_V$  tracking is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three attenuators. It is the difference in gain change between any two amplifiers with the contrast voltage, V21, at either 4V or 2V measured relative to an A<sub>V</sub> max condition V21 = 4V. For example, at A<sub>V</sub> max, the three amplifier gains might be 17.4 dB, 16.9 dB and 16.4 dB and change to 7.3 dB, 6.9 dB and 6.5 dB respectively for V21 = 2V. This yields the measured typical ±0.1 dB channel tracking.

Note 8: Brightness tracking error is measured with all three video channels set for equal gain. The measured value is limited by the resolution of the measurement

Note 9: When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit board is recommended. Video amplifier isolation tests also require this printed circuit board. The measured rise and fall times are effective rise and fall times, taking into account the rise and fall times of the generator.

Note 10: Measure output levels of either undriven amplifier relative to the driven amplifier to determine channel isolation. Terminate the undriven amplifier inputs.

## Typical Performance Characteristics $\,V_{CC}=\,$ 12V, $\,T_{A}=\,$ 25°C unless otherwise specified

TL/H/11238-2

## **Timing Diagram**

## Input/Output Stages

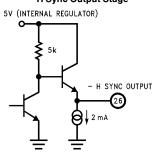

## - H Sync Output Stage

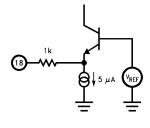

## **Composite Video Input**

TL/H/11238-6

### TL/H/11238-5

TL/H/11238-21

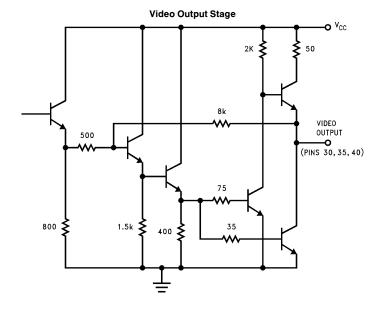

## Input/Output Stages (Continued)

## **Pin Descriptions**

V<sub>CC</sub> (Pins 2, 4, 6, 19, 31, 36, 41, 44)

All V<sub>CC</sub> pins must be externally wired together. For stable operation, each supply pin should be bypassed with a 0.01  $\mu$ F and a 0.1  $\mu$ F capacitor connected as close to the pin as is possible.

Contrast Cap (Pins 1, 3)

An external decoupling capacitor of value 0.1 µF should be connected between pins 1 and 3 for

contrast control.

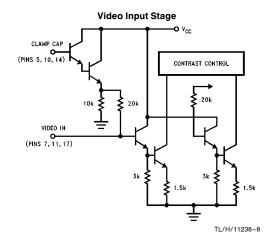

R Clamp Cap (Pin 5)

A 0.022  $\mu\text{F}$  to 0.1  $\mu\text{F}$  capacitor should be connected from this pin to ground. This capacitor allows

clamping of the red channel video signal to the reference black level.

B Clamp Cap (Pin 10)

A 0.022  $\mu$ F to 0.1  $\mu$ F capacitor should be connected from this pin to ground. This capacitor allows

clamping of the blue channel video signal to the reference black level.

G Clamp Cap (Pin 14)

A 0.022  $\mu$ F to 0.1  $\mu$ F capacitor should be connected from this pin to ground. This capacitor allows

clamping of the green channel video signal to the reference black level.

R Video In (Pin 7) This is the input for the red channel video signal, the signal should be AC coupled to the input through a 10 µF capacitor.

B Video In (Pin 11) This is the input for the blue channel video signal, the signal should be AC coupled to the input

through a 10  $\mu F$  capacitor.

G Video In (Pin 17) This is the input for the green channel video signal, the signal should be AC coupled to the input

through a 10 µF capacitor.

R A Gain (Pin 9) This is the gain adjustment pin for the red video channel. A 0V to  $4V_{DC}$  voltage is applied to this pin to

vary the gain of the red channel. Usually, the red channel is set for maximum gain and the gains of the blue and green channels are reduced relative to the red channel until white balance is achieved on

the CRT screen.

B Δ Gain (Pin 13) This is the gain adjustment pin for the blue video channel. A 0V to 4  $V_{DC}$  voltage is applied to this pin

to vary the gain of the blue channel.

G A Gain (Pin 15) This is the gain adjustment pin for the green video channel. A 0V to 4  $V_{DC}$  voltage is applied to this pin

to vary the gain of the green channel.

Compose Video Input

(Pin 18)

This is the sync separator input pin. For Sync on Green systems, the green channel video signal

should be AC coupled to pin 18 through a 0.1  $\mu$ F capacitor.

**Brightness Control**

Contrast Control (Pin 21)

(Pin 20)

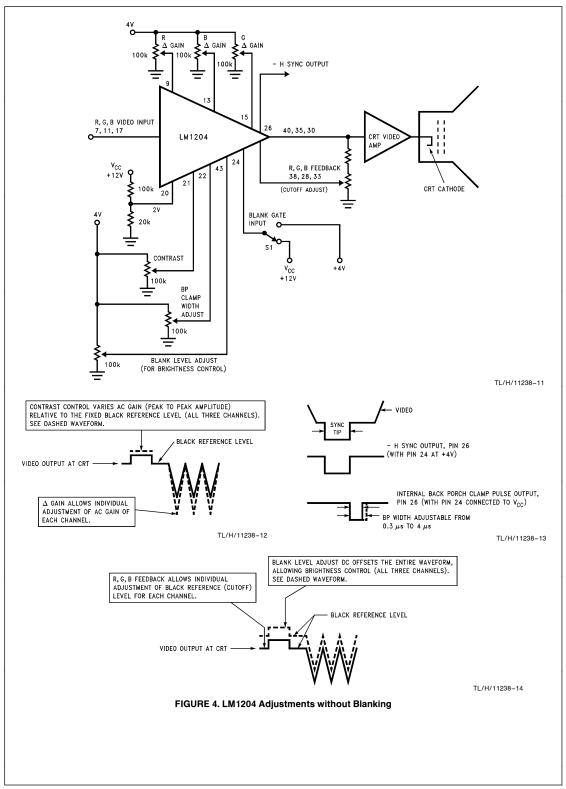

If the LM1204 is used without blanking then this pin should be biased at 2.0 V<sub>DC</sub>. Brightness control for all three video channels is now controlled by pin 43 (blank level adjust pin). See Figure 4. If the LM1204 is used with blanking then this pin allows the user to simultaneously DC offset the video

portion of the output signals of all three channels thus allowing brightness control (See Figure 5). This pin simultaneously controls the gain of all three video channels. A 0V to 4 V<sub>DC</sub> input voltage is

applied to this pin, with 0V corresponding to minimum gain (i.e., maximum attenuation of video signal)

and 4V corresponding to maximum gain (i.e., minimum attenuation of the video signal).

| Pin l | Descri | ptions | (Continued) |

|-------|--------|--------|-------------|

|-------|--------|--------|-------------|

Adjust (Pin 22)

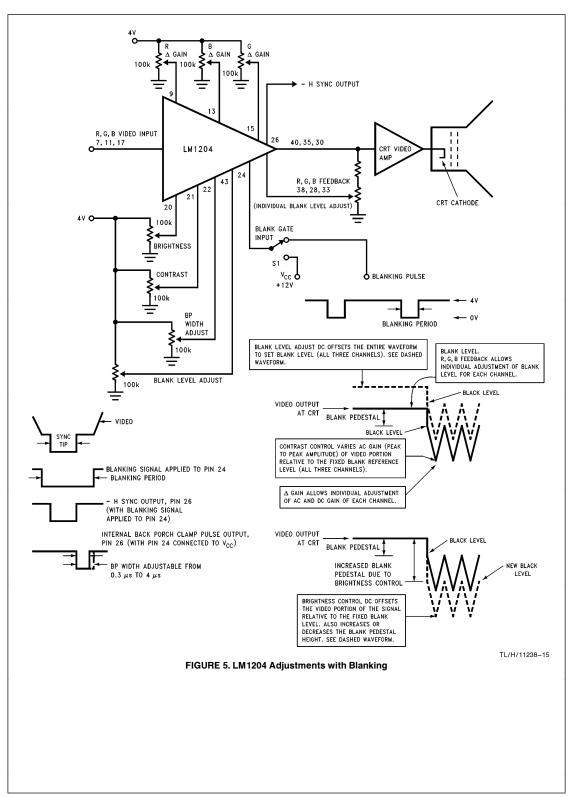

Back Porch Clamp Width The LM1204 provides DC restoration or clamping during the back porch interval of the video signal. The width of LM1204's internally generated back porch clamp signal can be varied by applying a 0V to 4 V<sub>DC</sub> voltage to this pin. The back porch clamp signal width can be varied from approximately  $0.3 \mu s$  to  $4.0 \mu s$  by applying 4V to 0.5 V respectively. By connecting the blank gate input pin (pin 24) to  $V_{CC}$ , the back porch clamp pulse can be monitored on the -H Sync output pin (pin 26). See Figures 4 and 5. By connecting pin 22 to V<sub>CC</sub>, the LM1204 functions as a non-gated amplifier requiring no clamping. See Section 4 under application hints for further information.

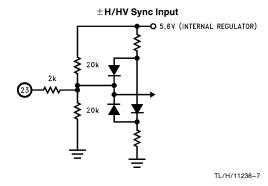

± H Sync In (Pin 23)

This is the external sync input pin, it accepts a negative or positive polarity signal, either horizontal sync or a composite sync (1.2 VPP minimum amplitude). The LM1204 also provides a negative polarity (TTL compatible) horizontal sync or composite sync output on pin 26. If the composite video input (pin 18) is not used then an H Sync signal should be AC coupled to this pin through a 0.1  $\mu$ F capacitor. The ±H Sync input has priority over the composite video input if both signals are present.

Blank Gate In (Pin 24)

This is the blank gate input pin. The LM1204 allows video blanking at the preamplifier. If blanking is desired then a TTL compatible, negative polarity blanking signal should be applied to this pin. During the blanking interval, all three video outputs are level shifted to the blank level set by the voltage at pin 43. If blanking is not required then, pin 24 should be biased at 4V.

Connecting pin 24 to V<sub>CC</sub> will cause pin 26 to output the internally generated back porch clamp signal. The user can observe the change in back porch width as the potential at pin 22 is varied (see Figures 4 and 5).

Integrator Cap (Pin 25)

A 0.1  $\mu$ F capacitor should be connected from this pin to ground. This capacitor allows the LM1204 to integrate the  $\pm H$  Sync input signal and genreate the proper polarity switch for -H Sync output.

- H Sync Out (Pin 26)

This output pin provides a negative polarity horizontal sync signal for other system uses. There is approximately 100 ns delay between the ±H Sync input signal at pin 23 and the -H Sync output signal at pin 26.

Connecting pin 24 to V<sub>CC</sub> will cause pin 26 to output the internally generated back porch clamp signal. The user can observe the change in back porch clamp pulse width as the potential at pin 22 is varied (See Figures 4 and 5).

G Feedback (Pin 28)

This is the cutoff adjustment input for the green video channel. The green video output signal from pin 30 is fed back to this input through a potentiometer thus allowing the user to individually adjust the cutoff (black reference) level for each gun. The signal level at this pin should be between 0.5V and 4V.

B Feedback (Pin 33)

This is the cutoff adjustment input for the blue video channel. The blue video output signal from pin 35 is fed back to this input through a potentiometer thus allowing the user to individually adjust the cutoff (black reference) level for each gun. The signal level at this pin should be between 0.5V and

R Feedback (Pin 38)

This is the cutoff adjustment input for the red video channel. The red video output signal from pin 40 is fed back to this input through a potentiometer thus allowing the user to individualy adjust the cutoff (black reference) level for each gun. The signal level at this pin should be between 0.5V and 4V.

G Video Output

This is the green channel video output.

(Pin 30)

B Video Output This is the blue channel video output. (Pin 35)

R Video Output

This is the red channel video output.

(Pin 40)

G Blank Clamp Cap A 0.022  $\mu$ F to 0.1  $\mu$ F capacitor should be connected from this pin to ground. This capacitor allows

(Pin 32)

blanking for the green video channel.

B Blank Clamp Cap

A 0.022  $\mu$ F to 0.1  $\mu$ F capacitor should be connected from this pin to ground. This capacitor allows blanking for the blue video channel.

(Pin 37)

A 0.022  $\mu$ F to 0.1  $\mu$ F capacitor should be connected from this pin to ground. This capacitor allows

This pin serves two functions depending on whether the LM1204 is used with blanking or without

R Blank Clamp Cap

(Pin 42)

blanking for the red video channel.

Blank Level Adjust (Pin 43)

blanking. If blanking is not selected then pin 20 should be biased at 2.0 VDC and pin 43 assumes the role of brightness control. Varying the potential at pin 43 will simultaneously DC offset the video output signals of all three channels (See Figure 4). If the LM1204 is used with blanking then during the blanking interval, all three video output signals will be level shifted to the blank level. The desired blank level can be set by adjusting the potential at pin 43. Brightness control is now made possible by varying the potential at pin 20. Adjusting the brightness control DC offsets the video portion of the

signal relative to the fixed blank level (all channels are affected simultaneously). See Figure 5.

GND (Pins 8, 12 16, 27,

29, 34, 39)

Ground. All ground pins must be connected to the ground plane.

## **Applications Hints**

The LM1204 is a wideband video amplifier system designed specifically for high resolution RGB CRT monitors. The device includes circuitry for DC restoration of video signals and also allows contrast and brightness control. DC restoration is done during the back porch interval of the video signal. An internal sync separator generates a back porch clamp signal either from a "Sync on Green" signal applied to the composite video input (pin 18) or from an externally supplied  $\pm H$  Sync signal . The LM1204 first looks at the  $\pm H$  Sync input (pin 23), if an external horizontal sync signal is not present then the device syncs off the composite video input. The internally generated back porch clamp pulse width is user adjustable.

A blanking function is also included. This allows the user to cutoff the beam current in the CRT's guns during the blanking interval thereby preventing horizontal retrace lines from being visible. Normally blanking is done by applying a high voltage pulse at the grid. However, blanking at the cathode using the LM1204 leads to ease of design and lowered cost.

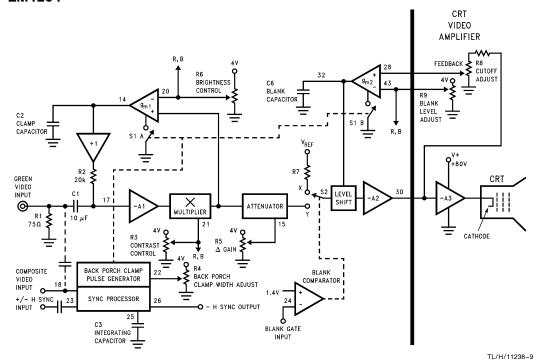

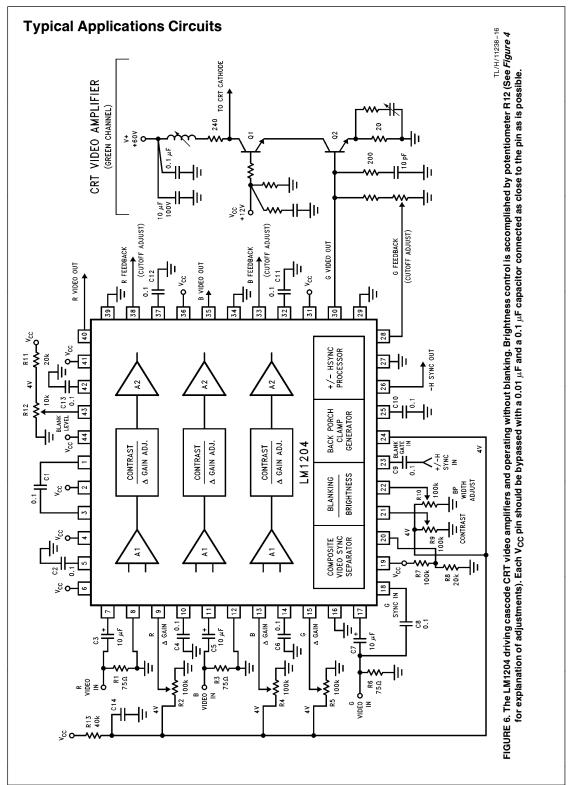

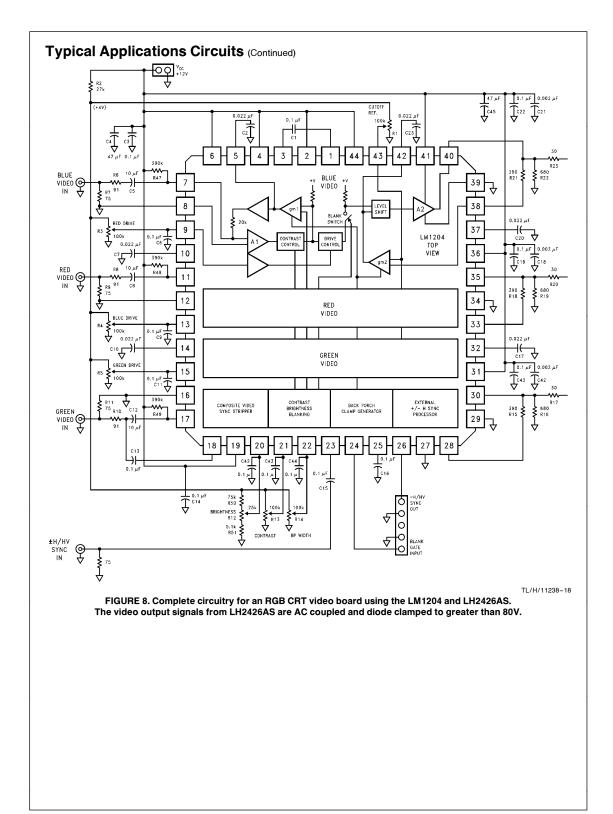

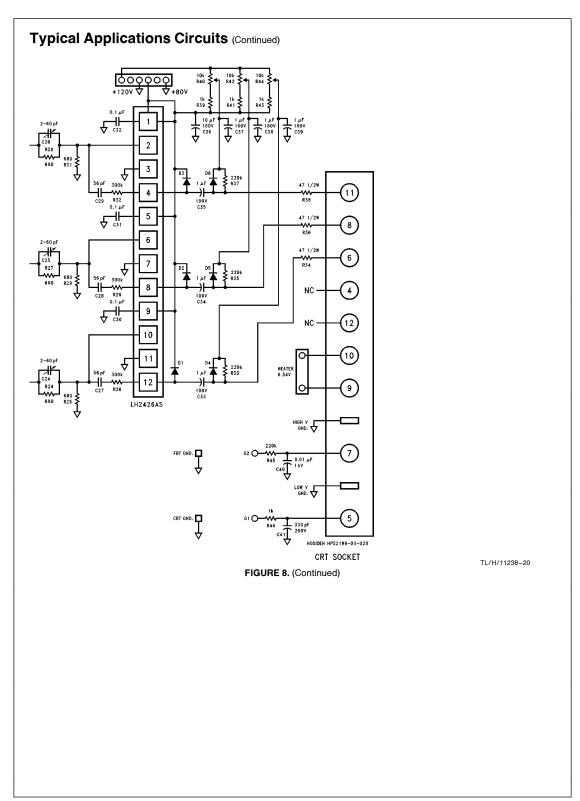

Figure 2 shows the block diagram of the green video channel and the control logic. The two modes of operation, with and without blanking, are described below in detail.

## 1.0 Operation without Blanking

For operation without blanking, the blank gate input (pin 24) should be connected to  $\pm 4V$ . This causes the blank comparator to connect switch S2 to position Y (See Figure 2).

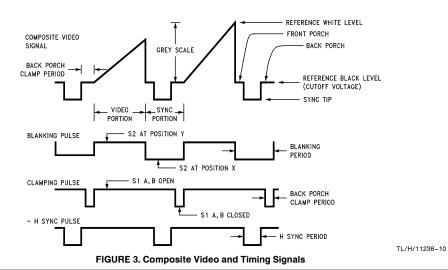

Furthermore, the brightness control input pin (pin 20) should be biased at a potential between 1V (Min) and 3.8V (Max), it is best to bias this pin at 2V. The video signal is AC coupled to the input of the LM1204 as shown for the green channel in Figure 2. During the back porch interval of the video signal (See Figure 3), the internally generated back porch clamping pulse goes low, causing switches S1A and S1B to be closed. The closure of S1A causes  $g_m1$  to charge capacitor C2 to a potential determined by the DC voltage at pin 20. This allows g<sub>m</sub>1 to set up an average DC bias for the AC coupled video signal at the input of A1. When the back porch clamping pulse is high, S1A and S1B are opened. With S1A open, g<sub>m</sub>1 is effectively disconnected from C2, C2 now holds the DC bias voltage. The transconductance stage gm1 therefore functions as a sample and hold device and holds the input of A1 at the desired DC bias.

The LM1204 uses black level clamping at the back porch of the video signal to accomplish DC restoration. The transconductance stage  $g_m2$  is enabled during the back porch clamp period to provide a sample and hold function. During the back porch clamp period, DC feedback from LM1204's video output is compared with the voltage set by potentiometer R9. Depending on A2's output voltage, C6 is either charged or discharged so that the feedback loop consisting of  $g_m2$  and A2 is stabilized and the output is clamped to the black level. All this occurs during the back porch clamp period. During the video portion of the signal,  $g_m2$  is disabled and C6 holds the fixed black level reference voltage. The beginning of each new line on the raster always starts from a fixed reference black level thus restoring the DC component of each line.

A2 is a summing amplifier that adds a DC offset component from  $g_{m2}$  to the video signal from the multiplier. Adjusting R9 will DC offset the output signals of all three channels thus providing brightness control. Individual cutoff adjust-

ment for each channel is done by varying the feedback voltage at each of the R, G and B feedback inputs (Pins 38, 28 and 33). For example, cutoff adjustment for the green channel is done by potentiometer R8 shown in *Figure 2*.

Adjusting the contrast control (potentiometer R3 in Figure 2) varies the peak to peak amplitude (includes sync tip if present) of all three video output signals relative to their black reference level. The  $\Delta$  Gain adjust (pins 9, 15 and 13 for R, G, and B channels respectively) allows the user to individually adjust the AC gain of each channel. For example the AC gain of the green channel is adjusted using potentiometer R5 as shown in Figure 2. Normally the red channel is set for maximum gain and the gains of the blue and green channels are reduced until white balance is achieved on the CRT monitor's screen. Figure 4 shows the adjustments for operation without blanking.

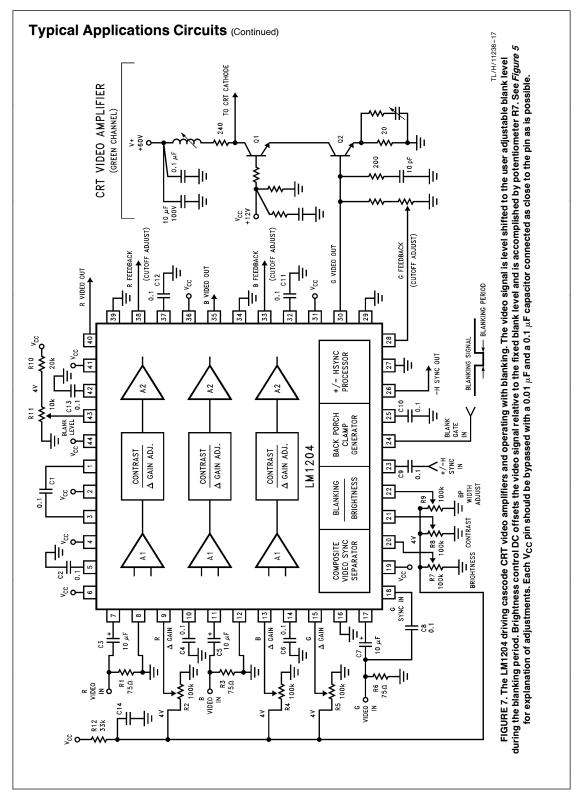

## 2.0 Operation with Blanking

Much of what was discussed in Section 1.0 also applies when the LM1204 is used with the blanking function. However, there are notable differences as described herein. For operation with blanking, a TTL compatible blanking signal must be applied to the blank gate input (pin 24).

During the blanking period, the blanking comparator connects switch S2 to position X (See Figure 2). This causes the LM1204 to level shift the video output signal to the blank level. Adjusting R9 will adjust the blank level of all three channels. Individual blank level adjustment for each channel is done by varying the feedback voltage at each of the R, G and B feedback inputs (pin 38, 28 and 33). In Figure 2 this is done by adjusting potentiometer R8 for the green channel

During the video portion of the video signal, S2 is connected to position Y. Brightness control is now accomplished by varying the potential at the brightness control pin (pin 20). Adjusting R6 offsets the video portion of all three output signals relative to the fixed blank level, restoring the DC level of the video signal. *Figure 5* shows the adjustments for operation with blanking.

## 3.0 Stability Considerations

For optimum performance and stable operation, a double sided PC board with adequate ground plane is essential. Moreover, soldering the LM1204 on to the PC board will yield best results. Each supply pin (pins 2, 4, 6, 19, 31, 36, 41 and 44) should be bypassed with a 0.01  $\mu F$  and a 0.1  $\mu F$  capacitor connected as close to the supply pin as is possible.

When driving the LM1204 from a  $75\Omega$  video source, the cable is terminated with  $75\Omega$  to minimize reflections caused by transmission line effects. However, the input impedance of LM1204 is capacitive and is also affected by the stray capacitance of the PC board. Thus the input impedance is a function of frequency. This changes the impedance of the cable termination. This can introduce overshoot and ringing in LM1204's pulse response. A  $100\Omega$  resistor in series with the blocking capacitor at the video input will minimize overshoot and ringing (see Figure~8). The value of the resistor is empirically determined.  $100\Omega$  is a good starting value.

Since the LM1204 is a wide bandwidth amplifier with high gain at high frequencies, the device may oscillate when driving a large capacitive/inductive load. To prevent oscillation, the amplifier's gain is rolled off at high frequencies. This is accomplished by an RC network comprised of a resistor in

## 3.0 Stability Considerations (Continued)

series with a capacitor connected from the video output pin to ground (see Test Circuit, Figure 1). A 110 $\Omega$  to 200 $\Omega$  resistor in series with 10 pF is quite adequate for most applications. However, if oscillations don't cease then the value of the resistor should be decreased or the value of the capacitor should be increased or a combination of the two.

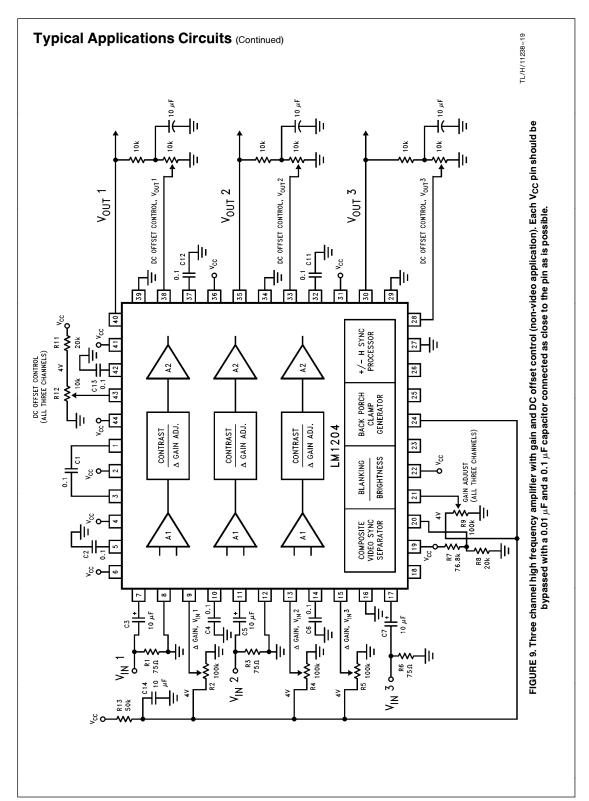

## Non-Gated High Frequency Application

By connecting the back porch width adjust pin (pin 22) to  $V_{CC}$ , the LM1204 functions as a non-gated amplifier requiring no sync or blanking signals. *Figure 9* shows a triple high frequency amplifier with variable gain and DC offset control. In this mode of operation, filtered DC feedback must be provided to pins 28, 33 and 38 as shown in *Figure 9*.

## LM1204

FIGURE 2. Block Diagram Showing Timing Circuitry and Green Video Channel

### Physical Dimensions inches (millimeters) +0.006 0.650 -0.000 +0.15 16.51 0 0.017±0.004 [0.43±0.10] TYP 45°X 0.045 PIN 1 IDENT 45°X 0.045 [1.14] 1 44 0.029±0.003 11 TYP [0.74±0.08] 0.610±0.020 [15.49±0.51] SEATING PLANE 18 28 0.020 [0.51] MIN TYP 0.050 [1.27] TYP 0.690-0.005 [17.53-0.13] 0.105±0.015 [2.67±0.38] TYP 0.500 [12.70] TYP 0.165-0.180 [4.19-4.57] TYP 0.004[0.10] V44A (REV K) Order Number LM1204V

NS Package Number V44A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408